CMOSAIC (European Project) could boost the computing performance of central processors by a factor 10 while consuming less energy.

3D microprocessors cooled from the inside through channels as thin as a human hair filled with a liquid coolant. Such is the solution currently being developed by researchers from the EPFL (Ecole polytechnique fédérale de Lausanne, Switzerland) and its sister organisation ETH Zurich to boost the performance of future computers. The CMOSAIC project, under the leadership of John R. Thome in Lausanne, aims to develop processors 10 times more powerful with as many transistors per cubic centimetre as there are neurons in the same volume of a human brain – a functional density greater than ever before. IBM has just signed a partnership to join the adventure.

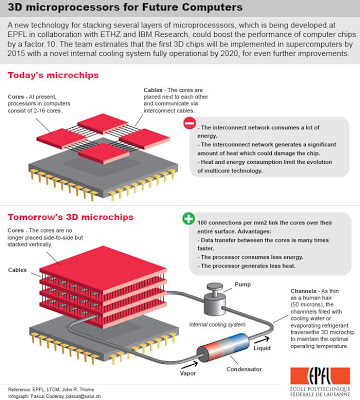

It will take a few years until 3D microchips equip consumer electronics. The initial 3D microprocessors should be fitted on supercomputers by 2015, while the version with an integrated cooling system should go to market around 2020.

3D processors build on the idea of multicores. However, the cores are stacked vertically rather than placed side-by-side as in current processors. The advantage is that the entire surface of the core can be connected to the next layer, through 100 to 10,0000 connections per mm2. Shorter and more numerous, these minute interconnects should ensure that data transfer is 10 times faster, while reducing energy consumption and heat.

Although 3D microprocessors will use up less energy and generate less heat, they will still warm up. This is why John R. Thome’s team is in charge of developing a revolutionary cooling system. Channels with a 50-micron diameter are inserted between each core layer. These microchannels contain a cooling liquid, which exits the circuit in the form of vapour, is brought back to the liquid state by a condenser and finally pumped back into the processor. Next year, a prototype of this cooling system will be implemented and tested under actual operating conditions – but without a processor

Brian Wang is a Futurist Thought Leader and a popular Science blogger with 1 million readers per month. His blog Nextbigfuture.com is ranked #1 Science News Blog. It covers many disruptive technology and trends including Space, Robotics, Artificial Intelligence, Medicine, Anti-aging Biotechnology, and Nanotechnology.

Known for identifying cutting edge technologies, he is currently a Co-Founder of a startup and fundraiser for high potential early-stage companies. He is the Head of Research for Allocations for deep technology investments and an Angel Investor at Space Angels.

A frequent speaker at corporations, he has been a TEDx speaker, a Singularity University speaker and guest at numerous interviews for radio and podcasts. He is open to public speaking and advising engagements.