Keynote speaker, IEEE Fellow Kevin Zhang, vice president of Intel’s Technology and Manufacturing Group, also Intel Director of Circuit Technology who led processor development from the 90-to-22 nanometer nodes explained “Intel is adding new circuitry, such as adaptive voltage control that increases yields over using fixed voltages, by making its analog circuits digital or at lease digitally assisted, and by exploring new materials for specific functions around the scaled CMOS cores.”

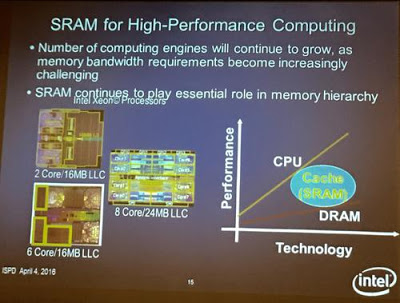

Zhang used the static-random-access-memory (SRAM) as his first example, because its architecture has remained the same for the last six generations, even though its use as on-chip caches for multi-core processors has become increasingly important (since DRAM speeds are not keeping pace with multi-core processor’s speeds).

“You need bigger and bigger SRAM caches on processor chips, despite they aging design, because DRAM has not been about to keep up with processor performance,” said Zhang. “You can mitigate the problems with SRAM with 3D, but the best way is merely to improve the size and performance of planar on-chip SRAM memory caches.”

Using SRAM as an example, its new architecture has been to get the best of both read/write worlds by “turning the supply voltage like a knob.” according to Zhang. Specifically, on-chip circuitry now changes the supply voltage when reading and writing, using lower voltage for write column section, and increasing supply voltage for reading column selection, thus mitigating the low-disturbance/high-disturbance problem, respectively, into a happy medium that improves the overall performance of the SRAM cell.

The power to the SRAM arrays, when idle, is also being cured, so that 99 percent of the array can be kept in sleep mode, while applying the low-or-high voltage supplies only to the SRAM cells being addressed at any one time—called dynamic sleep modes for SRAM.

Intel has also been continuously digitizing the analog functions on its processors, because analog circuits do not benefit from scaling like digital circuits. For instance the voltage scaling and temperature sensing circuits for power minimization and to prevent thermal runaway, respectively, have been converted to digital circuits. For instance, analog voltage controlled oscillators (VCOs) have been converted to Digital Voltage Controlled Oscillators (DCO), analog transistors for bipolar junction transistors (BJTs) for thermal runaway sensing, along with all the other analog functions inside the typical analog phase-locked-loop (PLL) that looks in processor frequencies.

Intel aims to keep its core processors in traditional CMOS, but surround it with new device architectures using new materials such as magnetic memories, Qubits, GaN transistors and whatever else proves to give leading edge advantages.

For circuits that Intel engineers have not yet figured a way to completely digitize, they are instead using hybrid mixed signal “digital assistance” techniques to optimize duty cycles, such as those used in its latest 14-nanometer processors to boost input/output speeds to 40-gigabits per second (GHz).

Brian Wang is a Futurist Thought Leader and a popular Science blogger with 1 million readers per month. His blog Nextbigfuture.com is ranked #1 Science News Blog. It covers many disruptive technology and trends including Space, Robotics, Artificial Intelligence, Medicine, Anti-aging Biotechnology, and Nanotechnology.

Known for identifying cutting edge technologies, he is currently a Co-Founder of a startup and fundraiser for high potential early-stage companies. He is the Head of Research for Allocations for deep technology investments and an Angel Investor at Space Angels.

A frequent speaker at corporations, he has been a TEDx speaker, a Singularity University speaker and guest at numerous interviews for radio and podcasts. He is open to public speaking and advising engagements.