The BlueGene/Q processor used in the Sequoia supercomputer IBM is building for Lawrence Livermore National Labs will employ the new feature, IBM disclosed in a paper at the Hot Chips event here. Sequoia is expected to deliver 20 petaflops when it is complete in 2012.

Transactional memory is a way of organizing related tasks into one big job for more efficient processing. It replaces the current practice of locking data until a complex job is done, an approach that can slow down other computer operations.

The former Sun Microsystems, now part of Oracle, implemented transaction memory in its Rock microprocessor aimed at large database computers, However, the Rock chips never shipped because the project was cancelled about the time Sun was acquired by Oracle.

A former Rock engineer said Sun tested the technique and found it had great advantages for some applications, but offered minimal help for others. It required almost no special hardware, he said.

IBM only implemented transactional memory within the confines of a single chip using a tagging scheme on the chip’s level-two cache memory. The tags are used to detect any load/store conflicts in data to be used in a so-called atomic transaction scheduled by the computer.

If no conflicts are found, the job can be processed. If conflicts do appear, the chip asks system software to resolve them.

Thanks to its use of fast on-chip memory, the IBM approach lowers latency when compared to traditional locking schemes even under conditions where there is high data contention.

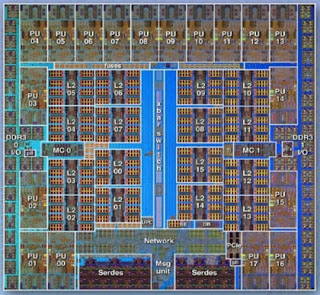

The IBM chip uses 18 cores, one just to process operating system tasks and another held in reserve as a spare. The cores are a custom circuit design based on the PowerEN core used in an IBM communications chip.

The rest of the BlueGene/Q processor was designed in an ASIC process given expectations for relatively low volume sales. The supercomputer may use as many as 100,000 of the chips. Running at 1.6 GHz, they deliver 204 Gflops at 55W, use 1.47 billion transistors and measure 19 x 19 mm.

If you liked this article, please give it a quick review on ycombinator or StumbleUpon. Thanks

Brian Wang is a Futurist Thought Leader and a popular Science blogger with 1 million readers per month. His blog Nextbigfuture.com is ranked #1 Science News Blog. It covers many disruptive technology and trends including Space, Robotics, Artificial Intelligence, Medicine, Anti-aging Biotechnology, and Nanotechnology.

Known for identifying cutting edge technologies, he is currently a Co-Founder of a startup and fundraiser for high potential early-stage companies. He is the Head of Research for Allocations for deep technology investments and an Angel Investor at Space Angels.

A frequent speaker at corporations, he has been a TEDx speaker, a Singularity University speaker and guest at numerous interviews for radio and podcasts. He is open to public speaking and advising engagements.